如何解决MySQL数据库连接超时问题?PHP环境下的应对策略

- 行业动态

- 2024-10-25

- 7

mysqli或

PDO的连接超时设置。使用

mysqli_options()函数来设置连接超时时间:,,“

php,$mysqli = new mysqli("localhost", "user", "password", "database");,$mysqli>options(MYSQLI_OPT_CONNECT_TIMEOUT, 30); // 设置连接超时时间为30秒,`

,,或者在使用PDO时,可以在DSN字符串中添加connect_timeout

参数:,,`

php,$dsn = "mysql:host=localhost;dbname=database;charset=utf8mb4";,$options = [, PDO::ATTR_ERRMODE => PDO::ERRMODE_EXCEPTION,, PDO::MYSQL_ATTR_INIT_COMMAND => "SET NAMES utf8mb4",, PDO::ATTR_TIMEOUT => 30 // 设置连接超时时间为30秒,];,$pdo = new PDO($dsn, "user", "password", $options);,“,,确保你的服务器和网络环境允许足够的时间进行连接,并检查防火墙和网络配置是否可能阻止了连接。

MySQL数据库连接超时在PHP开发中是一个常见的问题,它可能由多种因素引起,包括网络问题、服务器配置不当或代码实现错误,本文将详细探讨MySQL数据库连接超时的原因、解决方案以及如何通过优化来减少此类问题的发生。

原因分析

1、网络延迟或不稳定:如果客户端与数据库服务器之间的网络连接不稳定,或者存在较高的延迟,都可能导致连接超时。

2、服务器负载过高:当数据库服务器承受过多的请求压力时,可能会导致响应变慢甚至超时。

3、不合理的超时设置:默认情况下,MySQL和PHP都有自己的超时设置,这些设置如果过低,则很容易触发超时错误。

4、错误的数据库配置:包括但不限于最大连接数限制、等待时间过长等配置不当的情况。

5、代码层面的问题:如循环查询、未正确关闭数据库连接等情况也会导致资源耗尽而引发超时。

解决方案

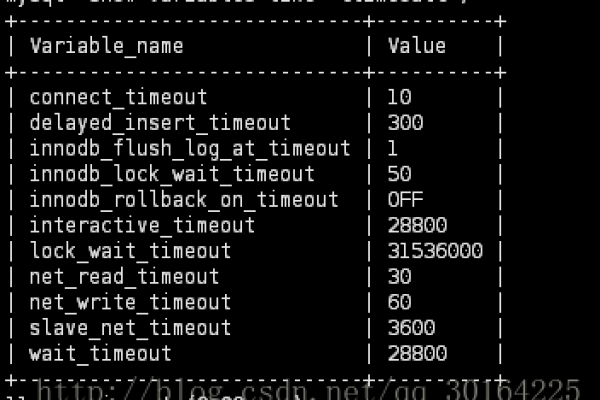

调整超时参数

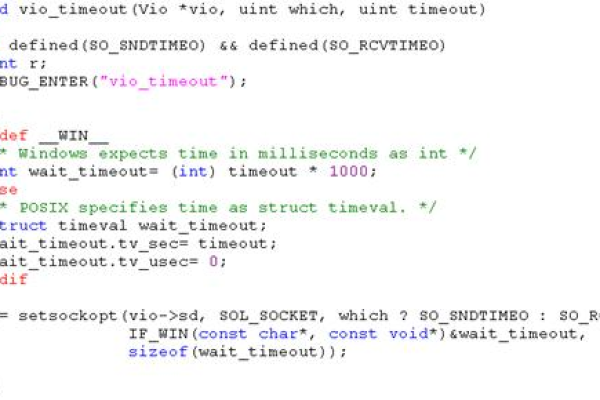

对于MySQL来说,可以通过修改wait_timeout和interactive_timeout两个参数来增加非交互式会话的最大空闲时间;对于PHP,则需要调整max_execution_time以允许更长的脚本执行时间。

示例(my.cnf配置文件):

[mysqld] wait_timeout=28800 interactive_timeout=28800

优化查询语句

确保SQL语句尽可能高效,避免全表扫描等操作,使用索引可以帮助加快查找速度。

定期检查并优化慢查询日志中的记录。

增加硬件资源

根据实际需求升级服务器规格,比如提高CPU核心数、内存容量等,以满足更高的并发访问需求。

使用连接池

通过建立持久化的数据库连接池,可以有效减少每次创建新连接所带来的开销,并且有助于更好地管理和维护数据库连接状态。

监控与报警

实施有效的监控系统,及时发现潜在的性能瓶颈或异常情况,并设置相应的警报机制以便快速响应处理。

实践案例

假设我们有一个基于LAMP架构的应用遇到了频繁的MySQL连接超时问题,经过初步诊断后发现主要是由于大量并发请求导致数据库服务器负载过高所致,为此,我们可以采取以下措施进行优化:

| 步骤 | 描述 |

| 1 | 调整MySQL服务器上的max_connections值至更高水平,同时适当延长wait_timeout和interactive_timeout的时长。 |

| 2 | 对现有业务逻辑进行全面审查,剔除不必要的复杂查询,简化数据模型结构。 |

| 3 | 引入Redis作为缓存层,减轻直接作用于主数据库的压力。 |

| 4 | 部署专用于读写分离的从库,分散读操作带来的负担。 |

| 5 | 利用PHP内置函数如mysqli_connect()中的connect_timeout选项设置合理的连接建立时限。 |

通过上述方法的应用,该网站成功地解决了之前存在的大部分性能瓶颈问题,用户体验得到了显著改善。

FAQs

Q1: 如何更改PHP中的最大执行时间限制?

A1: 在PHP代码中可以使用ini_set('max_execution_time', <秒数>);函数来临时改变当前脚本的最大运行时间限制,如果想要永久更改这个值,则需要编辑php.ini文件,找到max_execution_time项并将其设置为所需的秒数即可。

Q2: 何时使用持久连接而不是每次都重新建立新的数据库连接?

A2: 当应用程序需要频繁地与同一个数据库进行交互时(例如Web应用),采用持久连接能够显著提高效率,因为它避免了频繁打开关闭连接所带来的开销,但是需要注意的是,过多地保持打开状态而不释放无用的连接也会占用宝贵的系统资源,因此建议结合具体应用场景灵活选择是否启用持久连接功能。